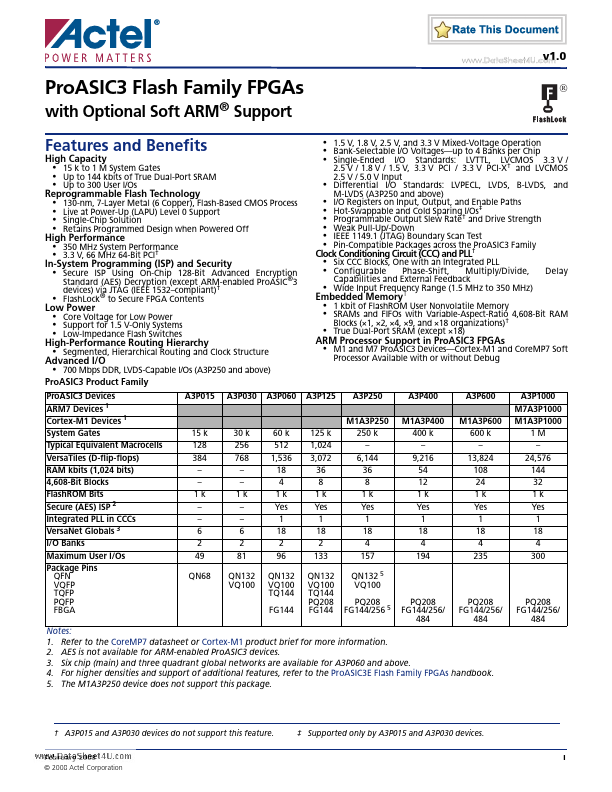

M1A3P400 Overview

Key Specifications

Mount Type: Surface Mount

Pins: 144

Max Operating Temp: 85 °C

Min Operating Temp: -40 °C

Key Features

- 15 k to 1 M System Gates

- Up to 144 kbits of True Dual-Port SRAM

- Up to 300 User I/Os ® Reprogrammable Flash Technology

- 350 MHz System Performance

- 3.3 V, 66 MHz 64-Bit PCI† Clock Conditioning Circuit (CCC) and PLL†

- 1.5 V, 1.8 V, 2.5 V, and 3.3 V Mixed-Voltage Operation

- Bank-Selectable I/O Voltages-up to 4 Banks per Chip

- Single-Ended I/O Standards: LVTTL, LVCMOS 3.3 V / 2.5 V / 1.8 V / 1.5 V, 3.3 V PCI / 3.3 V PCI-X† and LVCMOS 2.5 V / 5.0 V Input

- Differential I/O Standards: LVPECL, LVDS, B-LVDS, and M-LVDS (A3P250 and above)

- I/O Registers on Input, Output, and Enable Paths